取 BOOKE 精要,兼顾 E500 规范。 E500 规范是 BOOKE 的 32-bit 实现,更详细些,大部与 BOOKE 兼容。

BOOKE 对存储管理的规范较抽象,没有非常多的细节(比如 TLB 每项的结构必须如此等等),涉及细节则多以 E500 为例子。

1. 概述

E500 实现有两级 TLB,即:L1 TLB 和 L2 TLB。L1 TLB 可以理解为 L2 TLB 的部分缓存。访问 L1 TLB 的效率要比 L2 的效率高,相应的实现的花费也就高。L1 TLB 由硬件维护,不可编程精确控制。故下面的讨论皆针对 L2 TLB,为方便简称其为 TLB。

E500 没有对虚拟地址空间进行划分,即没有固定使用某段虚拟地址固定映射到某段物理地址 (MIPS,主要用于支持设备资源的固定映射以及方便内核对内存的管理)。而是引入了一个更灵活的设计:将 TLB 分为 TLB0 和 TLB1。

TLB0 即用于页映射的 TLB,可动态被替换,页大小固定为 4 KB。E500v1 实现为 2 路组相联,256 项;E500v2 实现为 4 路组相联,512 项。

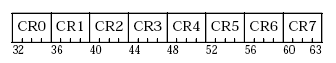

TLB1 则设计用于映射大页(比如 16MB, 256MB …),支持可变页大小,E500v1 可支持 9 个页大小(最大 256MB),E500v2 则支持 11 个页大小(最大 4GB)。使用时可将某项设为永驻 TLB1 (通过置 Invalidation Protection 位,简写为 IPROT 位),不会被动态替换,实现为全相联,共 16 项,可将其理解为用于映射 16 个段的可编程固定映射机制。